-

[미세공정WAR] 파운드리 산업의 미래(2)뇌피셜 IT 2023. 5. 11. 21:05

최근에 나온 AMD Ryzen 7000시리즈를 사용하는

AM5 고사양 메인보드(X670E)에서 소켓이 타버리는 문제가 발생하고 있어 한창 논란이다

이에 대하여 고전압이 문제이기에 메인보드 단에서 전압을 제한하는 BIOS까지 배포되고 있는 지경

그런데 말이다

과연 고전압이 문제인 것일까??

내가 보기엔 아니니까 이 칼럼이 작성되는 것이다. 이 모든 것의 원인은 바로 미세공정에 달려있다고 보는 쪽이다.

이를 이해하기 위해서는 ①공정(선폭) ②노광장비 ③양자 터널링 ④반도체 구조에 대하여 다뤄야 한다. 대기업 블로그가 아닌 개인 블로그에서 이만큼 고-품-격(High Quality and Class) 정보는 보기 힘드니 집중하길 바란다.3. 양자 터널링 효과(quantum tunneling effect)

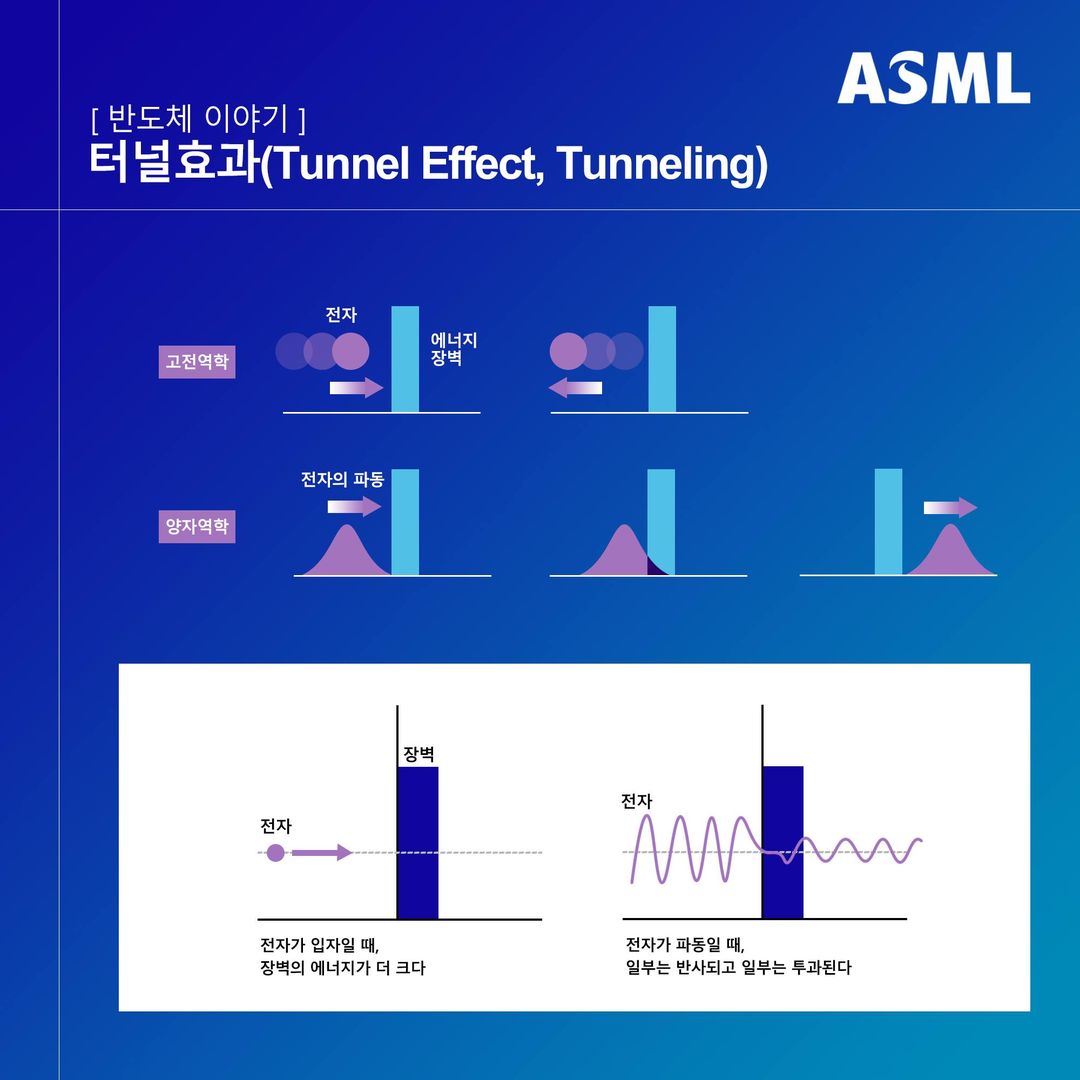

고전 물리학에서는 어떠한 물체가 벽으로 막혀있는 곳에서 반대편으로 나타나는 것은 불가능 하다. 그렇기 때문에 작용-반작용으로 물체는 벽에서 튕겨나오는 것이다. 이를 물리학 용어로 (거시물리학에서) 입자는 자신이 갖는 에너지보다 준위가 높은 에너지 장벽을 넘을 수 없다라고 한다.

그러나 양자역학에서는 새로운 사실이 발견되었다. (미시물리학에서) 충분히 작은 입자에서는 확률적으로 에너지 장벽을 뛰어넘는 현상이 관측되었는데, 이를 양자 터널링 효과라고 한다.

터널효과가 무엇인가(ASML) 여기서 관찰해 볼 Point는 ① 에너지 장벽이 얇을수록 양자 터널링 효과가 발생할 확률이 높아진다는 사실이다. 이 현상이 반도체에서 일어나면 어떻게 될까? 미세공정으로 갈수록, 전기가 흘러야 하는 회로가 아닌 그 밖으로 흘러나가는 전자(=누설전류; leakage current)가 많아진다는 것이다. ② 또한 회로가 정교하지 않을수록 (꾸불꾸불할 수록) 누설전류는 커진다고 알려져 있다.

에너지 장벽을 통과하는 전자를 표현한 에니메이션(wikipedia) 미세공정에서 누설전류(leakage current)가 많아지면서,

A. 공정미세화로 인한 전류 최적화보다, 실제로는 더 많은 전류가 필요하고

B. 누설전류 때문에 반도체가 오작동할 위험이 더 커졌으며 (이 때문에 방사선이 가득한 우주에서 쓰이는 반도체는 구세대 공정을 애용한다)

C. 특정소자는 일정 크기 이하로 줄이기 힘들다 (SRAM은 7nm 이하부터는 크기를 줄이기 어려운 한계에 직면했다)

D. 20nm 이하부터는 일반회로 또한 누선전류가 급증하였다

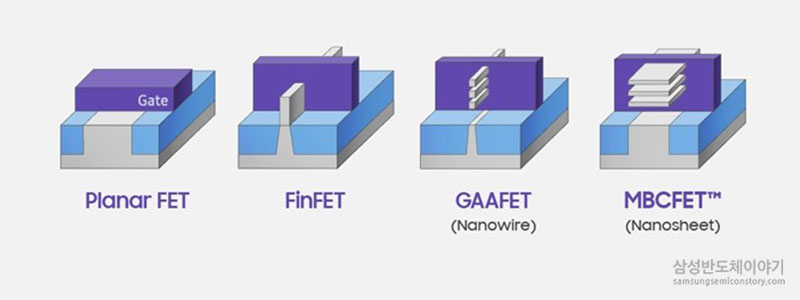

실제 반도체 미세공정에서는 30㎚ 미만의 공정에서는 누설전류가 급증하는 현상이 관측되었고, Intel은 22㎚부터, TSMC/삼성전자 등은 16/14㎚에서 FinFet이라는 새로운 반도체 구조를 도입하게 된다.4. 반도체 소자 구조

반도체(半導體 / Semi-conductor)란 무엇인가? 전기 전도율이 구리 같은 도체하고 애자, 유리 같은 부도체의 중간 정도인 물질을 말한다. 쉽게 전기가 흐르는 듯 안 흐르는 물체다 이말이다. 이런 특성 때문에 기본적으로 전기가 안 흐르지만, 전압을 가하게 되면 반도체는 전기가 흐르는 모습을 보여준다.

이러한 반도체를 최소 단위인 소자(Transistor/트랜지스터)로 구현하는 구조가 미세공정의 핵심이 되었다.

반도체 소자 구조의 발전(삼성반도체이야기) A. 기존에서는 평면(2D) 구조로 반도체는 구현되었다. 이를 Planar FET(장효과 트랜지스터; Field-Effect Transistor) 구조라고 부른다. 반도체에서 좌-우의 청색은 전류를 말하며, 위에 얹힌 Gate에 전압을 가할수록 가운데의 회색지대가 도체에 가까워져서 전류를 흐르게 한다. 이는 아래의 그림과 같은 원리로 보면 된다. 누르는 압력이 전압이라고 보면 된다.

FET 작동원리(wikipedia) 그러나 20㎚ 이하에서 Gate로 전압을 안 가하였는데도, (반도체 성질을 지닌) 회색지대를 일부 전자가 넘어가는 누선전류가 급증하게 되었다.

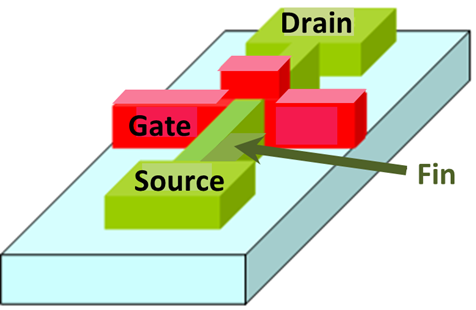

B. 그렇다면 Gate를 한 방향이 아닌 좌우위, 3면으로 구성하자는 아이디어가 FinFET(Fin : 물고기 지느러미)이며, Intel은 이를 3D Tri-Gate Transistor라고 부르기도 하였다. 흥미롭게도 이 구조는 원광대에 재직하던 이종호 교수가 개발한 기술이며, Intel이 22㎚ 반도체에서 상용화하여 적용하였다. (벌써부터 국뽕이 가슴 한켠을 넘어서 나의 태극기를 매단 주막의 주모가 술을 한동 나르고 있다. Do you know Kim-chi? Do you know Korea? Do you know FinFET?)

FinFET 구조(wikipedia) 누설전류가 흐를 공간이 1면으로 줄였기에 20㎚의 벽을 넘어, 지금은 4㎚의 공정으로 NVIDIA는 RTX4090/4080, AMD는 Ryzen 7950X/7800X 등을 생산하고 있다.

그런데 지금 파운드리(Foundry) 업계의 Apple인 TSMC가 3nm에서 고전하고 있다는 찌라시가 솔솔 들려오고 있다. 기존의 공정에서 기본적으로 75%~90%는 먹고가던 수율이 55%로 개박살 났다는 소문이다.

거기다가 뜬금없이 AMD의 AM5 소켓을 사용하는 메인보드의 Ryzen 7950X와 7800X3D 가 타버린다는 썰도 솔솔 나온다.

이 모든 것이 누설전류가 원인이라는 것이 필자의 의견이다. 기술적으로 4㎚부터는 단채널 효과(Short Channel Effect)로 Gate와 무관하게 누설전류가 흐르게 된다.

D. 그래서 4면의 전류흐름을 모두 통제하는 GAA(Gate All Around) 기술이 필요해진 것이다. 이렇게 되면 흐르는 전류를 더욱 더 미세하게 조정하게 되어, 누설전류를 최소화한다.

GAA 구조(skhynix) 해당 구조는 3㎚ 이하의 공정 기술에서 필수적인 기술이라고 여겨지고 있기에, 세계의 유수한 파운드리 업체인 TSMC, 삼성전자, Intel은 이 기술을 적용하기 위하여 노력하고 있다.

'뇌피셜 IT' 카테고리의 다른 글

[미세공정WAR] 파운드리 산업의 미래(3) (0) 2023.05.12 [미세공정WAR] 파운드리 산업의 미래(1) (1) 2023.05.06 [GPU WAR v2] AMD는 RX7000에서 플래그십이 멸망했나? (0) 2022.11.07 [CPU WAR] 22Q4 데스크탑 CPU 누가 저렴하게 생산할까? (1) 2022.10.04 [CPU WAR] 22Q4 데스크탑 CPU 관전 Point (0) 2022.09.29